Contents lists available at ScienceDirect

Sensors and Actuators: B. Chemical

# Optimized electrochemical breakdown etching using temporal voltage variation for formation of nanopores in a silicon membrane

Nguyen Xuan Chung<sup>a,b,1,\*</sup>, Hithesh Kumar Gatty<sup>a,1</sup>, Xi Lu<sup>a</sup>, Miao Zhang<sup>a,c</sup>, Jan Linnros<sup>a</sup>

<sup>a</sup> Nanosilicon Group, KTH Royal Technology Institute, 100 44 Stockholm, Sweden

<sup>b</sup> Department of Physics, Hanoi University of Mining and Geology, 18 Pho Vien, Duc Thang, Bac Tu Liem, Hanoi, Viet Nam

<sup>c</sup> Institute of Bioengineering, School of Engineering, Ecole Polytechnique Federale de Lausanne (EPFL), 1015 Lausanne, Switzerland

#### ARTICLE INFO

ABSTRACT

Keywords: Nanopore Electrochemical breakdown etching High-aspect-ratio Silicon membranes Dielectric breakdown etching is a well-known method of making nanopores on thin ( $\sim$ 50 nm) dielectric membranes. However, voltage driven translocation of biomolecules through such nanopores becomes extremely fast. For improved detection, for instance by the current blockage, a high-aspect-ratio nanopore could be beneficial for slowing down the translocation. High-aspect-ratio nanopore on silicon fabrication requires a well-controlled process and is dependent on specific crystal orientation, dopant type and resistivity of substrate. Therefore, an optimized method of processing high-aspect-ratio nanopores is necessary considering the advantage of a silicon membrane being able to be integrated with standard CMOS processing. Here, we present an optimized fabrication method for mass-producing a single and an array of nanopores on a thick ( $2 \mu m$ ) silicon device layer based on a silicon-on-insulator (SOI) wafer. A method of temporal voltage variation is exploited to optimize the etching parameters for the nanopore formation during electrochemical breakdown etching, diameters of nanopore around 12 nm have been achieved. Besides, the correlation between the parameters of etching and nanopore diameter is deduced. The processed high-aspect-ratio nanopore enables applications in single-molecule sensing such as DNA, exosomes, viruses, and protein markers. The developed process is inexpensive, fast and can be batch fabricated.

## 1. Introduction

Nanopores, in particular, solid-state nanopores with a diameter scale of 10 nm have gained considerable interest for their applications in various fields such as human genome sequencing, ion filtration with high selective character [1,2], nanoparticle detection [3–6], hemofiltration [7], protein sensing [8], and virus detection [9]. These nanopores are fabricated from various materials. Different diameter scales of nanopores are obtained by using different materials such as Al<sub>2</sub>O<sub>3</sub> [10, 11], graphene [12], silicon nitride [13–15], MoS<sub>2</sub> [16], HfO<sub>2</sub> [17] and silicon [18]. Another type of nanopore, called "biological pores", is derived from proteins, such as MspA [19,20], and  $\alpha$ -hemolysin [21]. In comparison between solid-state nanopores and biological nanopores, the solid-state nanopores show higher signal-to noise ratio when using a high sampling rate to record the signal [22–24]. Therefore, solid-state nanopores are found more stable at higher voltages and bandwidths. Among solid-state nanopores, the ones based on silicon offer many advantages due to its compatibility to be integrated into the standard silicon CMOS technology [25]. Mass-fabrication of silicon nanopore chips may therefore revolutionize single-molecule sensing-based research and clinical applications with high throughput and low-cost sensing devices. With nanopores on a silicon substrate, the detection of DNA translocation can be improved due to a sharper spike of current blockage [26]. To obtain a large array of nanopores with desired pore sizes for various target molecules, a variety of nanopore fabrication methods on silicon have been reported recently: Anisotropic KOH etching on pre-patterned silicon membranes by e-beam lithography were used to produce nanopores of diameters in the range of 10-100 nm [27–30]. Ling et al. used high laser power to fabricate pores with a large diameter scale, around 200 µm [28]. Nanopores on a thin silicon nitride (SiN) with a diameter of approx. 2 nm has been processed using controlled dielectric breakdown etching [31-33]. Nanopores have been processed in several other materials including silicon nitride membranes by a combination of e-beam lithography and reactive ion etching [34].

https://doi.org/10.1016/j.snb.2020.129323

Received 30 July 2020; Received in revised form 28 October 2020; Accepted 2 December 2020 Available online 29 December 2020 0925-4005/© 2020 Elsevier B.V. All rights reserved.

$<sup>^{\</sup>ast}$  Corresponding author at: Nanosilicon Group, KTH Royal Technology Institute, 100 44 Stockholm, Sweden.

E-mail address: nguyenxuanchung@humg.edu.vn (N.X. Chung).

<sup>&</sup>lt;sup>1</sup> Equal contribution.

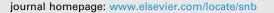

**Fig. 1.** Schematic of the voltage model to produce nanopores and nanopore formation in an SOI wafer. (a) Schematic of the voltage-time model with high voltage, transition and low bias regions for electrochemical breakdown etching to achieve a nanopore. (b) Schematic depicting UV lithography on SOI wafer to produce templates of the inverted pyramid structure. The templates are used for producing nanopores using the electrochemical breakdown etching.

However, e-beam lithography-based methods are relatively expensive and time-consuming. Anisotropic KOH etching suffers from large pore size variation inherited from the variation in membrane thickness and the lithography step. Furthermore, several methods are identified to slow down the translocation time of biomolecules such as piranha cleaning and atomic layer deposition of ZnO [35,36]]. Recently, our group has shown that a high-aspect-ratio nanopore can be used with a longer DNA translocation time [37].

To address the above-mentioned problems as well as to improve the aspect ratio of nanopore, we have earlier demonstrated a mass-fabrication of high-aspect-ratio nanopores in silicon by electrochemical etching with illumination [38]. Arrays of nanopores of diameters ranging from 8 nm to 100 nm with aspect ratio over 10 were fabricated. However, low reproducibility of pore sizes between batches due to the lack of breakdown process control hinders the further applications of this method. Although, an alternative approach of using illumination to generate electron-hole pairs to sustain electrochemical reaction was reported to decouple pore etching from the applied voltage in bulk silicon substrate [38]. Using illumination on a thin membrane often results in uncontrollable large pore size due to excessive amount of electron-hole pairs in the confined space [39]. Therefore, a nanopore etching method with a controllable pore size in a broad range and high reproducibility is still challenging.

In this work, we present a novel electrochemical etching method to fabricate nanopores on silicon membranes by using temporal voltage variation (time optimized multi-step-voltage model) to control the breakdown etching. This method is an illumination-free method and the electron-hole pairs in the silicon created by the avalanche effect under high voltage. This results in a high-aspect-ratio nanopore with high reproducibility. The novelty lies in the method of in-situ modulation of voltage and time duration according to the pore geometry to obtain a high-aspect- ratio and small nanopore diameter. This method is repeatable and the diameter of the nanopore correlates to the voltage model and the duration of etching. Using this method, we obtain nanopores with length of approx. 1000 nm and with a diameter below 10 nm. This method allows for a standardized processing method, which lowers the cost of production. The silicon chips containing the nanopores are processed in the clean room. Hence, inherently the yield is high. Moreover, the fast processing of nanopores using electrochemical breakdown etching and low cost method of processing has advantages in batch processing of silicon chips. The silicon nanopores can be processed in wafer-level and hence has the potential to scale-up. The processedhigh-aspect-ratio nanopore is suitable for a wide range of applications in biomolecule sensing such as DNA, exosomes, viruses, and protein markers. With this process, we could envision high throughput fabrication of nanopores (single as well as arrays) with accurate diameters.

## 2. Materials and methods

In this section, we present a detailed analysis of electrochemical breakdown etching. The novel part in this method is the variation of the applied electric voltage to control the geometry of the growing pore. This allows the user to have significant control over the process of producing high-aspect-ratio nanopores.

#### 2.1. The description of nanopore formation process

During the process of electrochemical etching, the dissolution of silicon occurs under anodic potentials when immersed in an HF solution. Positive charged carriers or holes  $(h^+)$  in silicon are generated by an electric breakdown in this reaction. Avalanche breakdown dominates in the moderately (or low) doped silicon, the free carriers in the space charge region (SCR) are accelerated by the high electric field and collide with crystal lattice thereby freeing the bound electrons. In this situation, the current density (J) is limited by the mass transport of the electrolyte [40]. Therefore, when J is less than a critical current density (which depends on the HF concentration, absolute temperature and the activation energy), the divalent reaction occurs [41]:

$$\mathrm{Si} + 2F^- + 2h^+ \rightarrow \mathrm{SiF}_2 \tag{1}$$

$$SiF_2 + 2HF \rightarrow SiF_4 + H_2 \tag{2}$$

where,  $h^+$  represents the holes in silicon. On the pyramid-structured silicon surface, the field strength increases with the decreasing radius of structure curvature, lowering the required voltage to trigger an electric breakdown. Thus, the breakdown can begin selectively at the pore tip. As the pore etching progresses, the radius of the pore tip decreases. As a result, a voltage lower than the initial one is needed to maintain breakdown etching selectively at the sharpest tip, which enables a minimized pore diameter. Each chip is etched by the voltage model in Fig. 1(a).

The voltage model is selected based on the experimental results of several iterations of electrochemical breakdown etching. Two constant voltage values corresponding to two regions of voltage named as highbias  $(V_{\mu})$  and low-bias  $(V_{\nu})$  regions are applied.  $V_{\mu}$  is used to initiate nanopores at the tip of inverted pyramids on the front side by creating a tip with a high curvature. However, from the previous report, for etching using backside illumination [18], high voltage coupled with illumination can generate an unexpectedly large amount of positive charges on

#### Table 1

Temporal voltage variation for investigating the best bias profile to obtain narrow nanopores on a silicon device layer in an SOI wafer.

| Region             | High bias   | Transition        | Low bias |  |  |

|--------------------|-------------|-------------------|----------|--|--|

| V <sub>b</sub> (V) | 13.5–18.0 V | Linearly variable | 7.0 V    |  |  |

| t(s)               | 13–14 s     | 20                | Variable |  |  |

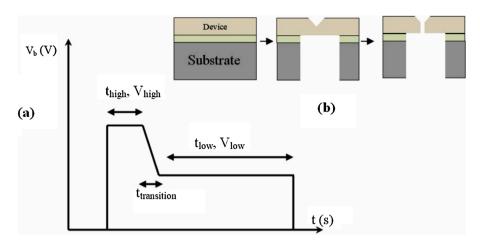

**Fig. 2.** Schematic of the etching setup. The SOI chip containing the template for nanopore formation is placed in between the two chambers. One of the chambers is filled with 5 %HF solution and the other is filled with NaCl and ethanol solution. The voltage is varied using an external circuit that is controlled by a Matlab program. The inset schematic shows the reaction occurring at the tip of the inverted pyramid structure.

the wall of the nanopores leading to uneven electric field distribution making the walls rough. Therefore, the electric field distribution around the tip of the inverted pyramid is carefully controlled to have a uniform electric field distribution during etching. The following variation of voltage  $(V_b) -$  time (t) as shown in Table 1, is observed to find optimal bias profile. Between high and low bias regions, durations of 20 s for transition region ( $t_{rous}$ ) is fixed, and the voltage value of the low bias region is fixed at 7.0 V for all experiments. A schematic of processing a high-aspect-ratio nanopore in the device layer of the silicon chip produced by UV lithography and KOH etching, then etched by electrochemical-breakdown method from the device layer is shown in Fig. 1(b).

#### 2.2. Electrochemical etching setup

The silicon on insulator chip containing the template for producing a nanopore is placed in between the two chambers. One of the chambers is filled with 5 %HF solution and the other is filled with NaCl and ethanol solution. Two platinum electrodes which are inert to aggressive electrolyte are connected to the two chambers and a voltage is applied between them. A power supply is connected to an external electronic circuit consisting of controller using a home-built MATLAB® program.

The processed chip is mounted on a home-built PTFE cell that is filled with 5 % HF: H<sub>2</sub>O: C<sub>2</sub>H<sub>5</sub>OH (1:8:3) solution on the device side of the chip (cis) and NaCl solution (9 mg/ml) on the handle layer of the chip (trans) as shown in Fig. 2. Two O-rings are contacted the both sides of the chip to avoid any leakage. When V<sub>b</sub> is applied between the two electrodes in the electrochemical cell, the bottom tip of the inverted pyramid experiences a stronger field strength due to high curvature and thin membrane thickness. This effect allows the electric field strength to reach the threshold of breakdown  $(3 \times 10^5 \text{ V/cm})$  at the bottom tip of the inverted pyramid as compared to a planar surface. In addition, the anisotropy of the etching, rate plays an important role in the formation of straight pores. The current density is the highest along  $(0 \ 0 \ 1)$  direction of the silicon crystal thus the pores tend to grow along the  $(0 \ 0 \ 1)$  direction since the current density equals to the critical current density due to the assumption that a tetravalent reaction occurs [41,42].

Inverted pyramid template processing: A series of chips with inverted pyramid templates are processed on 15 mm  $\times$  15 mm sized chips of an SOI wafer. A 4-inch-silicon wafer with 3 layers: device layer, n-type (2  $\pm$  0.5  $\mu$ m) with a resistance of 1–5  $\Omega$ .cm $^{-1}$ , buried oxide(BOX) layer (1  $\mu$ m) and handle silicon layer (500  $\pm$  25  $\mu$ m). A square opening with a size of 2  $\mu$ m  $\times$  2  $\mu$ m is created using UV lithography on the device layer. The inverted pyramid is formed using 30 %wt KOH for a total duration of 200 s at 80 °C. For the electrolyte contact with the device layer, a large square opening of the size 100  $\mu$ m  $\times$  100  $\mu$ m is etched by using DRIE from the back of the silicon substrate. The results of the ICP etching are checked by using an optical microscope to ensure that the residual silicon layer on the backside of the device is completely etched.

#### 2.3. Nanopore fabricated by electrochemical breakdown etching

After fabricating the front and the back sides of membranes, chips are cleaned by two types of RCA-cleaning solutions. The RCA-1 contains the mixture of NH<sub>4</sub>OH, H<sub>2</sub>O<sub>2</sub> and deionized water with a volume ratio of 0.2:0.2:1.0 to remove organic residuals on the surface of membranes. Next, chips are soaked inside a solution consisted of HCl, H<sub>2</sub>O<sub>2</sub> and deionized water, the volume ratio of this mixture is 0.2:0.2:1.0 for metallic contamination cleaning (RCA-2). The cleaning processes are conducted at 80 °C for 5 min. The electrochemical-breakdown-etching setup used to process nanopores is shown in Fig. 2. To control voltage and record current during etching, a homemade circuit with relays is operated by a Matlab script. All the etching processes are carried out at room temperature.

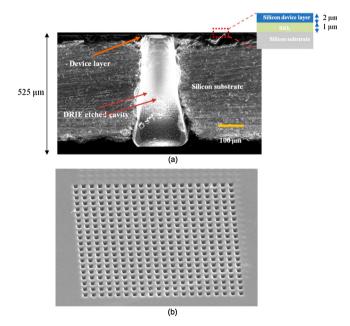

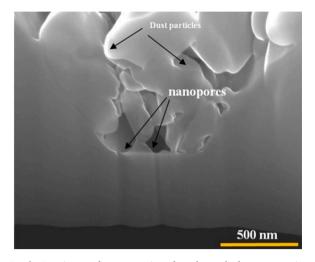

Fig. 3. Cross-sectional images of the nanopore and SOI chip, (a) Cross-section-EM image of an SOI wafer showing the deep-reactive-ion etched region of silicon substrate wafer that allows suspending a 2  $\mu$ m thick device layer. (b) SEM image of the device layer showing an array of 20  $\times$  20 inverted pyramids with a nanopore on each inverted pyramid processed by KOH etching and electro-chemical breakdown etching.

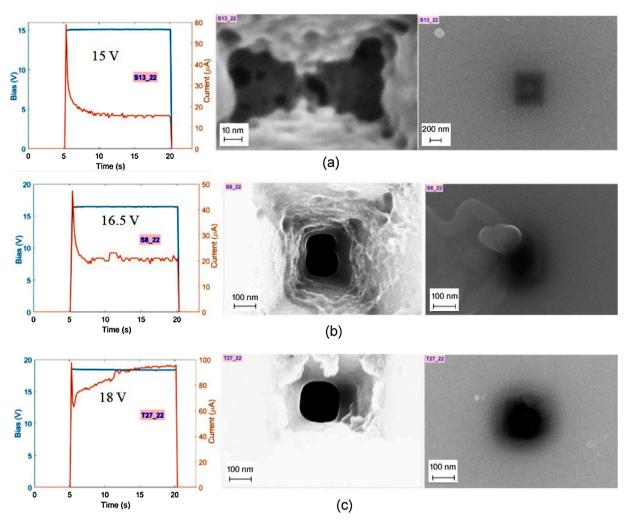

**Fig. 4.** A combination of images shows the results achieved during high voltage etching at several single voltages. In each panel (horizontal), left: voltage model (blue), current trace (red), middle: SEM image of nanopore on front side and right: SEM image of backside of etched chips. Panel (a): results of model of 15.0 V for 14 s on S13\_22 chip. The SEM image of the frontside shows about 30–40 nm wide nanopore. Panel (b): chips S8\_22 show clearer nanopore formation as etched by a bias of 16.5 V. Panel (c): chip T27\_22 shows a very clear large nanopore as the result of 18.0 V bias. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

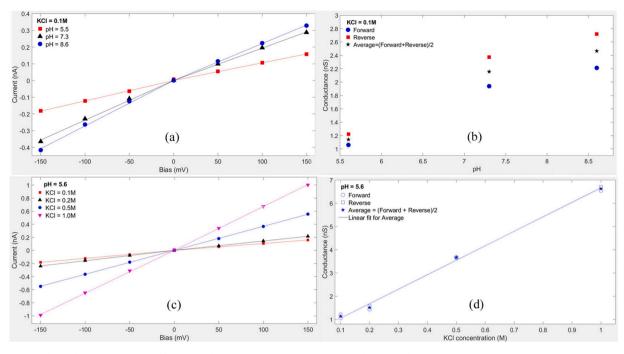

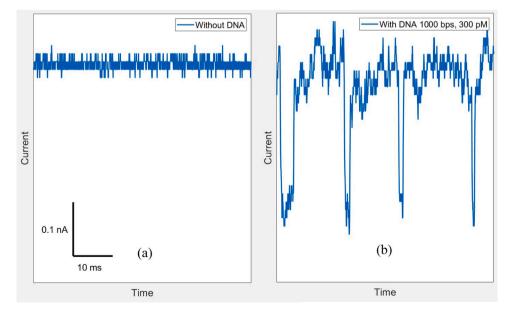

#### 2.4. Conductance measurements and DNA translocation experiment

In order to investigate the potential of these etched nanopores for DNA translocation, the chips at first are cleaned by piranha solution  $(H_2SO_4:H_2O_2 = 3:1)$  followed by RCA-1 at 80 °C for 5 min and RCA-2 at 80 °C for 5 min cleaning. Finally these nanopores are processed by oxygen plasma for 2 min for surface treatment. We believe that these steps increases the wetting of nanopores. After the cleaning steps, the conductance measurements are performed with KCl solutions of different concentrations and pH values as shown in Fig. 10(b) and 10 (d). In the next step, an experiment to investigate DNA translocation through the nanopore in terms of current blockage is carried out. Both conductance and DNA translocation experiments use a fast amplifier (40 kHz sampling rate) PICO 2 to generate bias and record current.

## 3. Results and discussion

The following section describes the electrochemical breakdown etching from twelve SOI wafers with 26 devices on each of them. Each chip is processed by the voltage-time model in Fig. 1(a). The modulation of voltage-time and its effect on the nanopore diameter are investigated. The roles of high bias, transition and low bias regions are investigated in detail and their effects on electrochemical breakdown etching will be

#### discussed.

The SEM image in Fig. 3(a) shows the cross-section of the SOI chip. A large-deep-reactive-ion-etched (DRIE) cavity is used for electrolyte filling that connects the nanopore on the device layer. The silicon substrate allows suspending a  $2 \,\mu$ m thick device layer that houses the nanopores. Fig. 3(b) shows the KOH etched template with nanopores distributed in an array on the device layer. To examine the cross-section profile and the length of the nanopore, the chip is cut and imaged using a focused ion beam (30KV, FEI Nova 200 dual beam system).

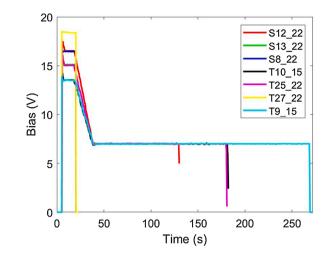

#### 3.1. The role of high bias region

To investigate the role of the high bias region, a rectangular voltage pulse is applied between the two electrodes. In this method, three voltage values, namely 15.0, 16.5 and 18.0 V are applied for etching three identical chips then they are investigated for nanopore formation by SEM. The experimental results are showed in Fig. 4. This section presents the role of low bias region on the nanopore formation by modulating its duration as the high bias region is fixed. The setup remained the same as in Fig. 2. As can be seen in Fig. 4, three identical samples are etched in the single high bias region. The chip S13\_22 is etched with a voltage of 15.0 V for 14 s. The SEM images from the front side and back side of the device layer indicate the initiation of a large

#### Table 2

The effect of high voltage on the diameter of nanopores.

| $V_b(V)$ | Duration $t$ (s) | $\mathbf{d}_{pore}$ from the backside of the device layer (nm) |

|----------|------------------|----------------------------------------------------------------|

| 15.0     | 14               | No pore                                                        |

| 16.5     | 14               | 50–70                                                          |

| 18.0     | 14               | 100–150                                                        |

nanopore in the range of 30–40 nm as can be seen in Fig. 4(a). However, there is no clear evidence of nanopore formation on the back side of the membrane. Two remaining chips are etched in the same condition as the first chip with a higher voltage, namely 16.5 and 18.0 V. As can be seen

from Fig. 4(b), a 100 nm wide nanopore is etched from the top side. The back-side image shows that a nanopore starts to appear with a size in the range 50–70 nm. The results of the sample T27\_22 etched by 18 V for 14 s is shown in Fig. 4c. From the current trace, it can be noted that the ionic current increases over time indicating an enlargement in the diameter of the nanopore. It could be possible to estimate the enlargement rate from the pore during etching. From the SEM images, we can observe that the diameter of nanopore on front side and back side are 170 nm and 100 nm, respectively. From the above results, we can see that breakdown etching starts at the tip of the inverted pyramid at 15.0 V. However, a large nanopore diameter is observed. Further tuning of the voltage may be necessary to achieve a small-diameter nanopore.

## Higher bias

Fig. 5. A schematic diagram of the tip of the inverted pyramid as the bias is increased in the high bias region.

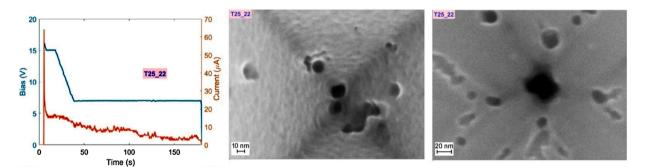

Fig. 6. The applied voltage model and the SEM images of nanopores on chip T25\_22. A combination of high and low voltage models to achieve a long and narrow-high-aspect-ratio nanopore with a duration of 142 s.

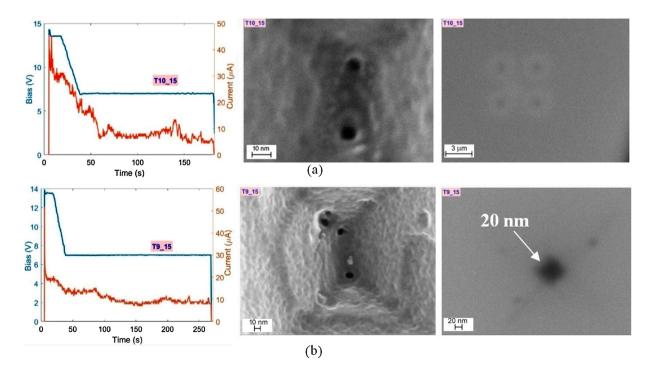

**Fig. 7.** Optimized etching model with high, transition and low bias regions. (a) SEM images of chip T10\_15 etched by voltage model with a short low bias region (left), the images of the front side (middle) and backside (right).(b)The optimal parameters for both high and low bias region to get small nanopore applied for chip T9\_15. Here a high bias region is set by 13.5 V and 14 s, while the low bias region relates to 7.0 V and 230 s.

**Fig. 8.** The SEM image of a cross-section of another etched nanopore using FIB on the T9\_15 chip showing the straight and high -aspect-ratio nanopores with a diameter of 20 nm.

Therefore, it can be concluded that the value of voltage and duration of high bias region are important parameters that affect on the overall radius of the nanopore at the end of the etching. A smaller initial diameter that can be achieved with high voltage could lead to a smaller diameter of nanopore at the exit. Hence, a voltage of 15.0 V or lower could be an optimum starting point for a smaller diameter nanopore to initiate at the tip of the inverted pyramid. This is an important value that would determine the further voltage-temporal model of the electrochemical breakdown etching.

The effect of high voltage on the diameter of the nanopore is reported in Table 2. An explanation of the advancement of the etching model during high voltage is schematically depicted in Fig. 5. It is observed that of the tip of the inverted pyramid enlarges as the bias is increased in the high bias region. The nanopore takes a "conical" shape with a large diameter at the entrance and a smaller diameter at the exit. When a voltage of 15.0 V for 14s is applied, it is observed that a small pore initiates on the front side. As the voltage is increased to 16.5 and 18.0 V in the same condition, the nanopore becomes larger. The proof for pore formation on the backside is clearer for a higher voltage. As we predict, a higher voltage results in a higher growth rate of a nanopore in the direction (001) and makes nanopore larger. Therefore, in order to obtain a smooth and straight profile of the nanopore, there is a need for a combination of a high bias and a low bias since a single model of high bias is not sufficient to create a cylindrical, straight and high-aspect -ratio nanopore.

#### 3.2. The role of low bias region

Following a high voltage model with a voltage of 15.0 V for 14 s and a 20s-transition region, a low-bias region with a voltage of 7.0 V is fixed and a variable duration is investigated.

The effect of a long low-bias region is shown in Fig. 6 where the applied voltage model and the SEM images of nanopores on chip T25\_22 are displayed. A combination of a high and a low voltage models to achieve a high-aspect-ratio nanopore with a duration of 142 s becomes apparent. The front side and back side of pore are approx. 15 nm and approx. 25 nm, respectively, indicating an outward conical structure of the nanopore. Therefore, the low voltage appears to continue "drilling" the nanopore on the direction (001) much faster than on other directions.

#### 3.3. Optimized and predictive etching parameters

To etch a high-aspect-ratio nanopore with a cylindrical, straight, and

**Fig. 9.** Etching voltage model after optimization of the etching process for seven devices. Configuration of voltage to the etching time, with the diameter of the nanopore showing various nanopore diameters.

narrow wall, there is a need for an optimized voltage temporal model for the electrochemical breakdown etching. In this section, optimized and predictive etching by the combination of high and low voltage model is described. As can be seen in Figs. 4 and 6, the diameter of the nanopore on the frontside mainly depends on the high bias region (both duration and voltage value), while that on the backside relates to the low bias region (also both duration and voltage value). The smaller diameter relates to a lower voltage and shorter duration. However, if the duration is too short, the nanopore is not completely etched. Therefore, an optimum value of etching parameter is needed. As shown in Fig. 7a, under low voltage duration of 144 s, the small nanopore (around 8 nm) is seen, but there is no proof of nanopore formation on the backside (low magnification). However, if the low voltage is maintained up to 230 s, as shown in Fig. 7b, the nanopore on the frontside is almost similar to that in the previous figure, but there is clear evidence for the existence of a nanopore on the backside of the membrane with a diameter around 20 nm. Fig. 8 shows an SEM image of the cross-section of a single inverted pyramid obtained from FIB etching. The image shows the crosssection of the device layer with a straight profile of the nanopores with a diameter of 25 nm. The etching of the device using KOH resulted in an inverted pyramid with a depth of 1.4 µm and the length of the nanopore is approx. 600 nm.

Seven chips from different batches of wafers are etched and their bias profiles are plotted in Fig. 9 , their diameter values are listed in Table 3.

The variation of the high bias region and the transition region is from 13.5 to 18.0 V and the transition time is 0 s or 20 s. The steady-state time is from 0 s to 230 s. The diameter variation with the optimized etching is small with clear proof of nanopore on both back and front sides. For our SOI wafer, the optimal high bias region is found to be 13.5 V for 13 s and followed by a low voltage of 7.0 V with a duration of 230 s. It should also be noted that the optimization model is subjected to several parameters such as the doping concentration, temperature, orientation of the wafer, the resistivity etc. Therefore, a careful estimate is necessary to reproduce the results reliably and effectively.

The temporal-voltage model for optimization of the electrochemical breakdown etching to produce narrow, cylindrical nanopores could help in applications for biosensing, physical nanopore arrays etc., and could replace a more common conical nanopore [43].

In the batch of samples, a nanopore with a diameter around 15 nm is selected to measure the conductance. The conductance measurements is performed on the nanopore using KCl buffer with the concentration of 0.1 M under 3 different pH values, i.e., 5.5, 7.3 and 8.6, the results are shown in Fig. 10(a). The current-bias relation is showed in Fig. 10(a) for 3 different pHs, while variations of conductance for different pH values

**Fig. 10.** (a) The relation between current and bias for KCl concentration of 0.1 M for 3 pH values, namely 5.5, 7.3 and 8.6. (b) The conductance at different pHs are deduced from the linear fittings of the dataset from panel (a). (c) The ionic current at various KCl concentrations with a constant pH of 5.6. It is seen that as the concentration increases the conductance increases. (d) The linear relation between the KCl concentration and the conductance.

| Table 3                                                                         |            |

|---------------------------------------------------------------------------------|------------|

| The detailed study of voltage, and the relation to the diameter of the nanopore | : <b>.</b> |

| No | Chip   | V <sub>H</sub><br>(V) | t <sub>H</sub><br>(s) | t <sub>trans</sub><br>(s) | V <sub>L</sub><br>(V) | t <sub>L</sub><br>(s) | d <sub>front</sub><br>(nm) | d <sub>back</sub><br>(nm) |

|----|--------|-----------------------|-----------------------|---------------------------|-----------------------|-----------------------|----------------------------|---------------------------|

| 1  | S13_22 | 15.0                  | 14                    | 0                         | 0                     | 0                     | 30–40                      | -                         |

| 2  | S8_22  | 16.5                  | 14                    | 0                         | 0                     | 0                     | 100                        | 50-70                     |

| 3  | T27_22 | 18.0                  | 14                    | 0                         | 0                     | 0                     | 170                        | 100                       |

| 4  | S12_22 | 15.0                  | 13                    | 20                        | 7                     | 92                    | 20                         | 10                        |

| 5  | T25_22 | 15.0                  | 13                    | 20                        | 7                     | 142                   | 15                         | 30                        |

| 6  | T9_15  | 13.5                  | 13                    | 20                        | 7                     | 230                   | 12                         | 20                        |

| 7  | T10_15 | 13.5                  | 13                    | 20                        | 7                     | 144                   | 8                          | Blur                      |

are shown in Fig. 10(b). The conductance increases for higher pH concentrations but the dependence is not linear. The rectification effect is found by using linear fitting functions for 2 regimes, namely positive (forward) and negative (reverse) biases. We observe an increase in nanopore conductance with increasing pH, as shown in Fig. 10(b). This can be attributed to the increased osmotic flow induced current due to increased negative surface charge at high pH [44].

The conductance of a nanopore with a diameter of 15 nm under different KCl concentrations is investigated. For a pH of 5.6, four KCl concentrations, namely 0.1, 0.2, 0.5 and 1.0 M are used. The characteristic of the nanopore at different KCl concentrations is shown in Fig. 10(c) and 10 (d). The variation of ionic current to bias at different

**Fig. 11.** The ionic current of the nanopore with and without DNA. (a) the ionic current across the nanopore when a voltage of 600 mV is applied. (b) When ds DNA of 1000 bps is inserted into the cis chamber of the chip. The amplitude is measured to be approx. 250 pA and the duration of event is approx. 1 ms.

KCl concentrations is shown in Fig. 10(c) and the variation of conductance with KCl concentration is shown in Fig. 10(d). The nanopore conductance increases with the concentration of KCl, indicating the detected current is indeed the ionic current through the nanopore.

We performed biosensing experiments to verify nanopore for DNA translocation. A single nanopore with diameter of approx. 15 nm is selected, KCl 1.0 M solution is used as a solvent to dilute DNA strands (300 pM with 1000 bps) under a bias of 600 mV. Fig. 11(a) shows the ionic current trace when 1.0 M KCl buffer is used, while Fig. 11(b) shows current blockage duration around few ms with an amplitude of around 250 pA. Because of this translocation rate, the amplifier with moderate bandwidth can be used for single molecule detection using these nanopores. This allows for a several applications of the nanopores such as protein sensing, exosome detection and virus translocation detection. However, the big challenge of this nanopore is its enlargement under high bias and high laser illumination, so the bias amplitude and illumination dose must be considered when molecule translocation through nanopores is investigated.

### 4. Conclusion

In summary, we present for the first time a novel method of optimized electrochemical breakdown etching for producing nanopores in a silicon substrate with high aspect ratio using temporal voltage variation. The method presented in this report is low-cost, fast and requires minimum control parameters. The optimal profile of bias allows to fabricate nanopore with diameter down to 10 nm. The wafer level processing method allows for several chips to be fabricated at once allowing for a low-cost chips. In addition, formation of nanopores using electrochemical etching is fast (approx. 20 min). Both single and array of nanopores can be processes with this method. The correlation between bias profile and diameter of nanopore is found and can be used to make desired nanopores. The voltage model with two bias regions results in clear nanopore formation, the relation between voltage model (both voltage value and duration) and diameter of the nanopore is clearly seen: longer duration and higher voltage leads to larger nanopores. The model could be useful for producing cylindrical, high-aspect-ratio nanopores. In future, we plan to integrate a feedback control system that would allow the formation of nanopores using the temporal voltage control method. This would allow us to process many nanopores in a repeatable and reliable way within a short duration of time.

#### Authors' contribution

Nguyen Xuan Chung: System installation, experiment, data process, writing, submission and revision. Hithesh Kumar Gatty: System installation, experiment, data process, writing and revision. Xi Lu: Experiment and revision. Miao Zhang: System Installation and revision. Jan Linnros: Supervision, revision and funding.

#### **Declaration of Competing Interest**

The authors report no declarations of interest.

#### References

- J. Vidal, M.E. Gracheva, J.-P. Leburton, Electrically tunable solid-state silicon nanopore ion filter, Nanoscale Res. Lett. 2 (2) (2007) 61.

- [2] D. Mancinelli, C. Hallé, Nano-filtration and ultra-filtration ceramic membranes for food processing: a mini review, J. Membr. Sci. Technol. 5 (140) (2015) 2.

- [3] O.N. Assad, N. Di Fiori, A.H. Squires, A. Meller, Two color DNA barcode detection in photoluminescence suppressed silicon nitride nanopores, Nano Lett. 15 (1) (2015) 745–752.

- [4] O.N. Assad, T. Gilboa, J. Spitzberg, M. Juhasz, E. Weinhold, A. Meller, Lightenhancing plasmonic-nanopore biosensor for superior single-molecule detection, Adv. Mater. 29 (9) (2017) 1605442.

- [5] A.H. Squires, J.S. Hersey, M.W. Grinstaff, A. Meller, A nanopore-nanofiber mesh biosensor to control DNA translocation, J. Am. Chem. Soc. 135 (44) (2013) 16304–16307.

- [6] J. Shim, G.I. Humphreys, B.M. Venkatesan, J.M. Munz, X. Zou, C. Sathe, K. Schulten, F. Kosari, A.M. Nardulli, G. Vasmatzis, et al., Detection and quantification of methylation in DNA using solid-state nanopores, Sci. Rep. 3 (2013) 1389.

- [7] W.H. Fissell, A. Dubnisheva, A.N. Eldridge, A.J. Fleischman, A.L. Zydney, S. Roy, High-performance silicon nanopore hemofiltration membranes, J. Membr. Sci. 326 (1) (2009) 58–63.

- [8] Y. Wu, K. Chuah, S. Vivekchand, K. Gaus, P.J. Reece, A.P. Micolich, J.J. Gooding, Nanopore blockade sensors for ultrasensitive detection of prostate-specific antigen in human whole blood, Nat. Commun. 10 (2109) (2019).

- [9] B.M. Venkatesan, B. Dorvel, S. Yemenicioglu, N. Watkins, I. Petrov, R. Bashir, Selective detections of single-viruses using solid-state nanopores, Adv. Mater. 21 (27) (2009) 2771–2776.

- [10] B.M. Venkatesan, B. Dorvel, S. Yemenicioglu, N. Watkins, I. Petrov, R. Bashir, Highly sensitive, mechanically stable nanopore sensors for DNA analysis, Adv. Mater. 21 (27) (2009) 2771–2776.

- [11] G. Pardon, H.K. Gatty, G. Stemme, W. van der Wijngaart, N. Roxhed, Pt-Al<sub>2</sub>O<sub>3</sub> dual layer atomic layer deposition coating in high aspect ratio nanopores, Nanotechnology 24 (1) (2012) 015602.

- [12] S. Garaj, W. Hubbard, A. Reina, J. Kong, D. Branton, J. Golovchenko, Graphene as a subnanometre trans-electrode membrane, Nature 467 (7312) (2010) 190–193.

- [13] W. Choi, E.-S. Jeon, K.-Y. Chun, Y.-R. Kim, K.-B. Park, K.-B. Kim, C.-S. Han, A lownoise silicon nitride nanopore device on a polymer substrate, PLoS One 13 (7) (2018) e0200831.

- [14] B.I. Karawdeniya, Y.N.D. Bandara, J.W. Nichols, R.B. Chevalier, J.R. Dwyer, Surveying silicon nitride nanopores for glycomics and heparin quality assurance, Nat. Commun. 9 (1) (2018) 1–8.

- [15] D.S. Talaga, J. Li, Single-molecule protein unfolding in solid state nanopores, J. Am. Chem. Soc. 131 (26) (2009) 9287–9297.

- [16] D. Estrada, Detection of methylation on dsDNA using nanopores in MoS<sub>2</sub> membrane, Nanoscale 9 (39) (2017) 14836–14845.

- [17] J. Shim, J.A. Rivera, R. Bashir, Electron beam induced local crystallization of HfO<sub>2</sub> nanopores for biosensing applications, Nanoscale 5 (22) (2013) 10887–10893.

- [18] T. Schmidt, M. Zhang, S. Yu, J. Linnros, Fabrication of ultra-high aspect ratio silicon nanopores by electrochemical etching, Appl. Phys. Lett. 105 (12) (2014) 123111.

- [19] A.H. Laszlo, I.M. Derrington, J.H. Gundlach, MspA nanopore as a single-molecule tool: from sequencing to SPRNT, Methods 105 (2016) 75–89.

- [20] D. Deamer, M. Akeson, D. Branton, Three decades of nanopore sequencing, Nat. Biotechnol. 34 (5) (2016) 518–524.

- [21] M. Boukhet, F. Piguet, H. Ouldali, M. Pastoriza-Gallego, J. Pelta, A. Oukhaled, Probing driving forces in aerolysin and α-hemolysin biological nanopores: electrophoresis versus electroosmosis, Nanoscale 8 (43) (2016) 18352–18359.

- [22] A. Fragasso, S. Schmid, C. Dekker, Comparing current noise in biological and solidstate nanopores, ACS Nano 14 (2) (2020) 1338–1349.

- [23] S. Howorka, Z. Siwy, Nanopore analytics: sensing of single molecules, Chem. Soc. Rev. 38 (8) (2009) 2360–2384.

- [24] T. Ma, J.-M. Janot, S. Balme, Track-etched nanopore/membrane: from fundamental to applications, Small Methods 4 (9) (2020) 2000366.

- [25] J.K. Rosenstein, M. Wanunu, C.A. Merchant, M. Drndic, K.L. Shepard, Integrated nanopore sensing platform with sub-microsecond temporal resolution, Nat. Methods 9 (5) (2012) 487.

- [26] M. Tsutsui, K. Yokota, T. Nakada, A. Arima, W. Tonomura, M. Taniguchi, T. Washio, T. Kawai, Silicon substrate effects on ionic current blockade in solidstate nanopores, Nanoscale 11 (10) (2019) 4190–4197.

- [27] A. Storm, J. Chen, X. Ling, H. Zandbergen, C. Dekker, Fabrication of solid-state nanopores with single-nanometre precision, Nat. Mater. 2 (8) (2003) 537–540.

- [28] S. Wu, S.R. Park, X.S. Ling, Lithography-free formation of nanopores in plastic membranes using laser heating, Nano Lett. 6 (11) (2006) 2571–2576.

- [29] T. Deng, J. Chen, W. Si, M. Yin, W. Ma, Z. Liu, Fabrication of silicon nanopore arrays using a combination of dry and wet etching, J. Vacuum Sci. Technol. B 30 (6) (2012) 061804.

- [30] S.R. Park, H. Peng, X.S. Ling, Fabrication of nanopores in silicon chips using feedback chemical etching, Small 3 (1) (2007) 116–119.

- [31] H. Kwok, K. Briggs, V. Tabard-Cossa, Nanopore fabrication by controlled dielectric breakdown, PLoS One 9 (3) (2014) e92880.

- [32] K. Briggs, H. Kwok, V. Tabard-Cossa, Automated fabrication of 2-nm solid-state nanopores for nucleic acid analysis, Small 10 (10) (2014) 2077–2086.

- [33] E. Beamish, H. Kwok, V. Tabard-Cossa, M. Godin, Precise control of the size and noise of solid-state nanopores using high electric fields, Nanotechnology 23 (40) (2012) 405301.

- [34] D.V. Verschueren, W. Yang, C. Dekker, Lithography-based fabrication of nanopore arrays in freestanding sin and graphene membranes, Nanotechnology 29 (14) (2018) 145302.

- [35] S. Cabello-Aguilar, S. Balme, A. Abou Chaaya, M. Bechelany, E. Balanzat, J.-M. Janot, C. Pochat-Bohatier, P. Miele, P. Dejardin, Slow translocation of polynucleotides and their discrimination by α-hemolysin inside a single tracketched nanopore designed by atomic layer deposition, Nanoscale 5 (20) (2013) 9582–9586.

- [36] S. Balme, P.E. Coulon, M. Lepoitevin, B. Charlot, N. Yandrapalli, C. Favard, D. Muriaux, M. Bechelany, J.-M. Janot, Influence of adsorption on proteins and amyloid detection by silicon nitride nanopore, Langmuir 32 (35) (2016) 8916–8925.

- [37] H.K. Gatty, C.X. Nguyen, M. Zhang, I. Sychugov, J. Linnros, Wafer-level fabrication of individual solid-state nanopores for sensing single DNAs, Nanotechnology 31 (355505) (2020).

- [38] T. Schmidt, M. Zhang, I. Sychugov, N. Roxhed, J. Linnros, Nanopore arrays in a silicon membrane for parallel single-molecule detection: fabrication, Nanotechnology 26 (31) (2015) 314001.

- [39] M.S. Khan, J.D. Williams, Fabrication of solid state nanopore in thin silicon membrane using low cost multistep chemical etching, Materials 8 (11) (2015) 7389–7400.

- [40] V. Lehmann, The physics of macropore formation in low doped n-type silicon, J. Electrochem. Soc. 140 (10) (1993) 2836.

- [41] V.M. Dubin, Formation mechanism of porous silicon layers obtained by anodization of monocrystalline n-type silicon in HF solutions, Surf. Sci. 274 (1) (1992) 82–92.

- [42] M. Zhang, Silicon Nanopore Arrays: Fabrication and Applications for DNA Sensing, KTH Royal Institute of Technology, 2018 (Ph.D. Thesis).

- [43] S. Zeng, C. Wen, P. Solomon, S.-L. Zhang, Z. Zhang, Rectification of protein translocation in truncated pyramidal nanopores, Nat. Nanotechnol. 14 (11) (2019) 1056–1062.

- [44] Y. Ma, L.-H. Yeh, S. Qian, pH-regulated ionic conductance in a nanopore, Electrochem. Commun. 43 (2014) 91–94.

**Nguyen Xuan Chung** was a Ph.D. student at University of Amsterdam between 2012 and 2017 with a research field of optical properties of silicon nanocrystals and co-doping effects in these nanocrystals. After that, he studied nanopore fabrication by electrochemical etching method and DNA translocation investigation through nanopores during his postdoctoral research at Department of Applied Physics until January 2020. Now he is a lecturer of Physics at Department of Physics, Hanoi university of Mining and Geology, Vietnam.

Hithesh Kumar Gatty graduated from KTH royal institute of Technology in micro and nanotechnology. His Ph.D. thesis was on wafer-level fabrication of gas sensors. He has worked in several research centers across Europe including ARCES, Italy IMEC Belgium. His expertise lies in development of sensors for Single molecule detection.

Xi Lu is currently a Ph.D. student in Jan Linnros' group at KTH Royal Institute of Technology. She received M.S. degree in 2019 from Harbin Institute of Technology. Her main research direction is fabrication and application of solid-state nanopores.

Miao Zhang received her PhD degree from KTH Royal Institute of Technology in 2018. The subject of her research was a development of electrochemical method to fabricate silicon nanopore arrays for fluorescence single-molecule detection. Currently she is working as a postdoc in EPFL on the topic of super-resolution microscopy on characterization of electrochemical properties of defects in 2D materials.

Jan Linnros received his Ph.D. in Physics (ion beam processing of materials) from Chalmers University of Technology (Göteborg, Sweden) in 1986. After a post-doc at Bell Labs, Murray Hill, he joined the Swedish Institute of Microelectronics in Stockholm to work on semiconductor material and device characterization. In 1993 he accepted a research position at Royal Institute of Technology and was appointed full professor in 2001. He is an active teacher and initiated/headed a master program in Nanoelectronics/ Nanotechnology. He has published ~200 scientific papers in international journals. Recent projects include the use of silicon nanostructures in bio-molecule sensing (nanowires) and DNA sequencing (nanopores) and for modifying surface properties. A main scientific break-through has been PL spectroscopy of individual silicon quantum dots.